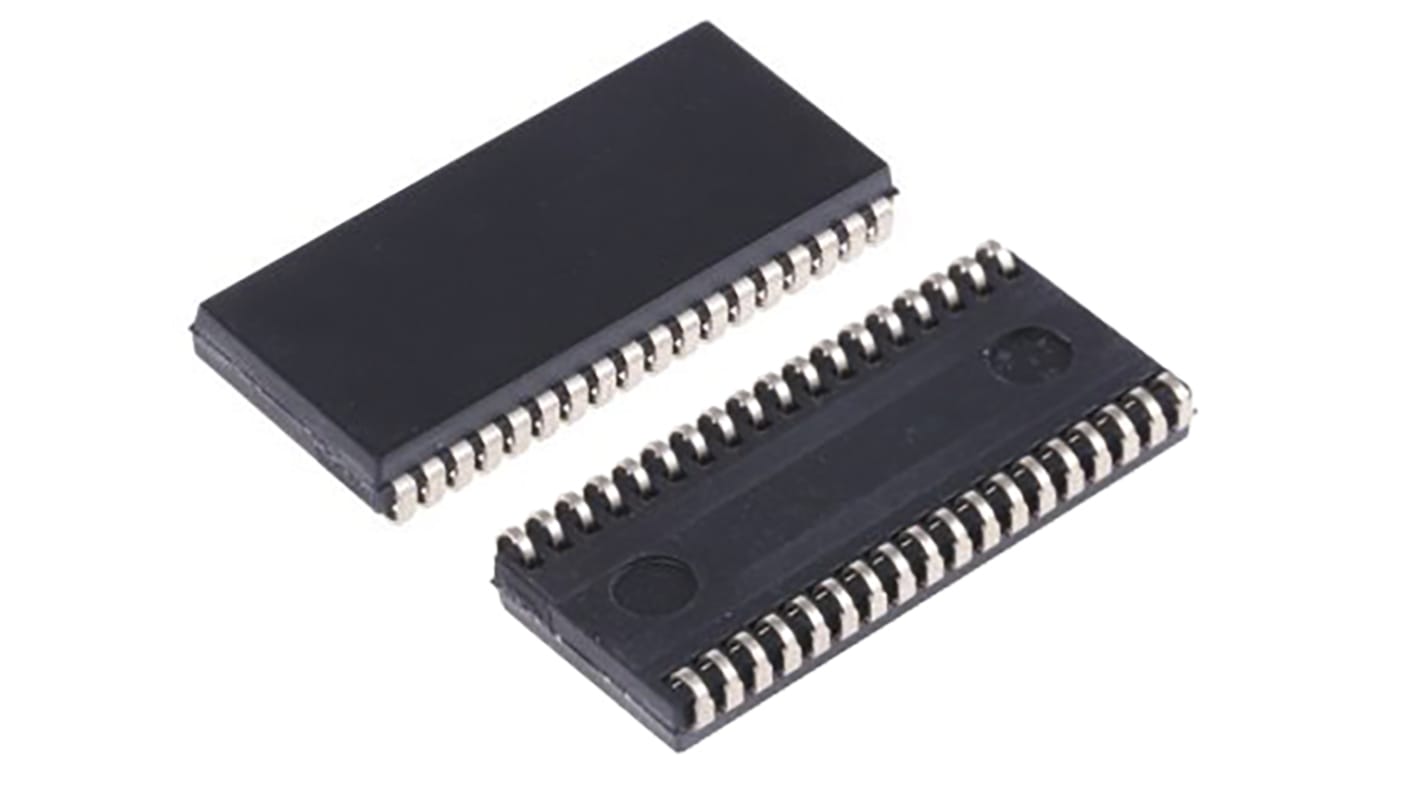

Infineon 4 MB SRAM 512K, 8 / Wort, SOJ 36-Pin

- RS Best.-Nr.:

- 182-3295

- Herst. Teile-Nr.:

- CY7C1049GN-10VXI

- Hersteller:

- Infineon

Zwischensumme (1 Stange mit 19 Stück)*

€ 76,513

(ohne MwSt.)

€ 91,808

(inkl. MwSt.)

VERSANDKOSTENFREIE Lieferung für Bestellungen ab € 100,00

Vorübergehend ausverkauft

- Versand ab 23. November 2026

Sie benötigen mehr? Benötigte Menge eingeben und auf „Lieferverfügbarkeit überprüfen“ klicken.

Stück | Pro Stück | Pro Stange* |

|---|---|---|

| 19 + | € 4,027 | € 76,51 |

*Richtpreis

- RS Best.-Nr.:

- 182-3295

- Herst. Teile-Nr.:

- CY7C1049GN-10VXI

- Hersteller:

- Infineon

Technische Daten des gezeigten Artikels

Datenblätter und Anleitungen

Rechtliche Anforderungen

Informationen zur Produktgruppe

Finden Sie ähnliche Produkte, indem Sie ein oder mehrere Eigenschaften auswählen.

Alle auswählen | Eigenschaft | Wert |

|---|---|---|

| Marke | Infineon | |

| Produkt Typ | SRAM | |

| Speicher Größe | 4MB | |

| Anzahl der Wörter | 512K | |

| Anzahl der Bits pro Wort | 8 | |

| Zugriffszeit max. | 10ns | |

| Timing Typ | Asynchron | |

| Montageart | Oberfläche | |

| Gehäusegröße | SOJ | |

| Pinanzahl | 36 | |

| Länge | 0.93mm | |

| Höhe | 0.12mm | |

| Normen/Zulassungen | RoHS | |

| Alle auswählen | ||

|---|---|---|

Marke Infineon | ||

Produkt Typ SRAM | ||

Speicher Größe 4MB | ||

Anzahl der Wörter 512K | ||

Anzahl der Bits pro Wort 8 | ||

Zugriffszeit max. 10ns | ||

Timing Typ Asynchron | ||

Montageart Oberfläche | ||

Gehäusegröße SOJ | ||

Pinanzahl 36 | ||

Länge 0.93mm | ||

Höhe 0.12mm | ||

Normen/Zulassungen RoHS | ||

- Ursprungsland:

- US

Der CY7C1049GN ist ein leistungsstarkes CMOS-Fast-Static-RAM-Gerät, das als 512 K Wörter pro 8 Bit organisiert ist. Datenschreibvorgänge werden ausgeführt, indem die Eingänge Chip Enable (CE) und Write Enable (WE) LOW bestätigt werden, während die Daten auf E/A0 über E/A7 und die Adresse auf A0 über A18-Stifte bereitgestellt werden. Datenlesungen werden durchgeführt, indem die Eingänge für Chip Enable (CE) und Output Enable (OE) LOW bestätigt werden und die erforderliche Adresse auf den Adresszeilen angegeben wird. Die Lesedaten sind auf den E/A-Leitungen (E/A0 bis E/A7) zugänglich. Alle E/A (E/A0 bis E/A7) werden in einem Zustand mit hoher Impedanz während der folgenden Ereignisse platziert: Das Gerät wird deaktiviert (CE HIGH) Das Steuersignal OE wird de-assert.

Hohe Geschwindigkeit

tAA = 10 ns

Niedrige aktive und Standby-Ströme

Aktiver Strom: ICC = 38 mA typisch

Standby-Strom: ISB2 = 6 mA typisch

Betriebsspannungsbereich: 1,65 V bis 2,2 V, 2,2 V bis 3,6 V und

4,5 V bis 5,5 V

1,0 V Datenspeicherung

TTL-kompatible Eingänge und Ausgänge

Bleifreie 36-polige SOJ- und 44-polige TSOP II-Gehäuse

Verwandte Links

- Infineon 4 MB SRAM 512K SOJ 36-Pin

- Infineon 4 MB SRAM 512K 100 MHz 36-polig gegossen SOJ/44-polig TSOP II 44-Pin

- Infineon 4MBit SRAM-Speicherbaustein 512k 100MHz SOJ 36-Pin

- Infineon 4 MB SRAM 256K 100 MHz SOJ 44-Pin

- Infineon 4 MB SRAM 512K, 8 / Wort 22-Pin

- Infineon 4 MB SRAM 512K TSOP II 32-Pin

- Infineon 4 MB SRAM 512K SOIC 32-Pin

- Infineon 4096 kB SRAM 512K 1 MHz SOJ 36-Pin