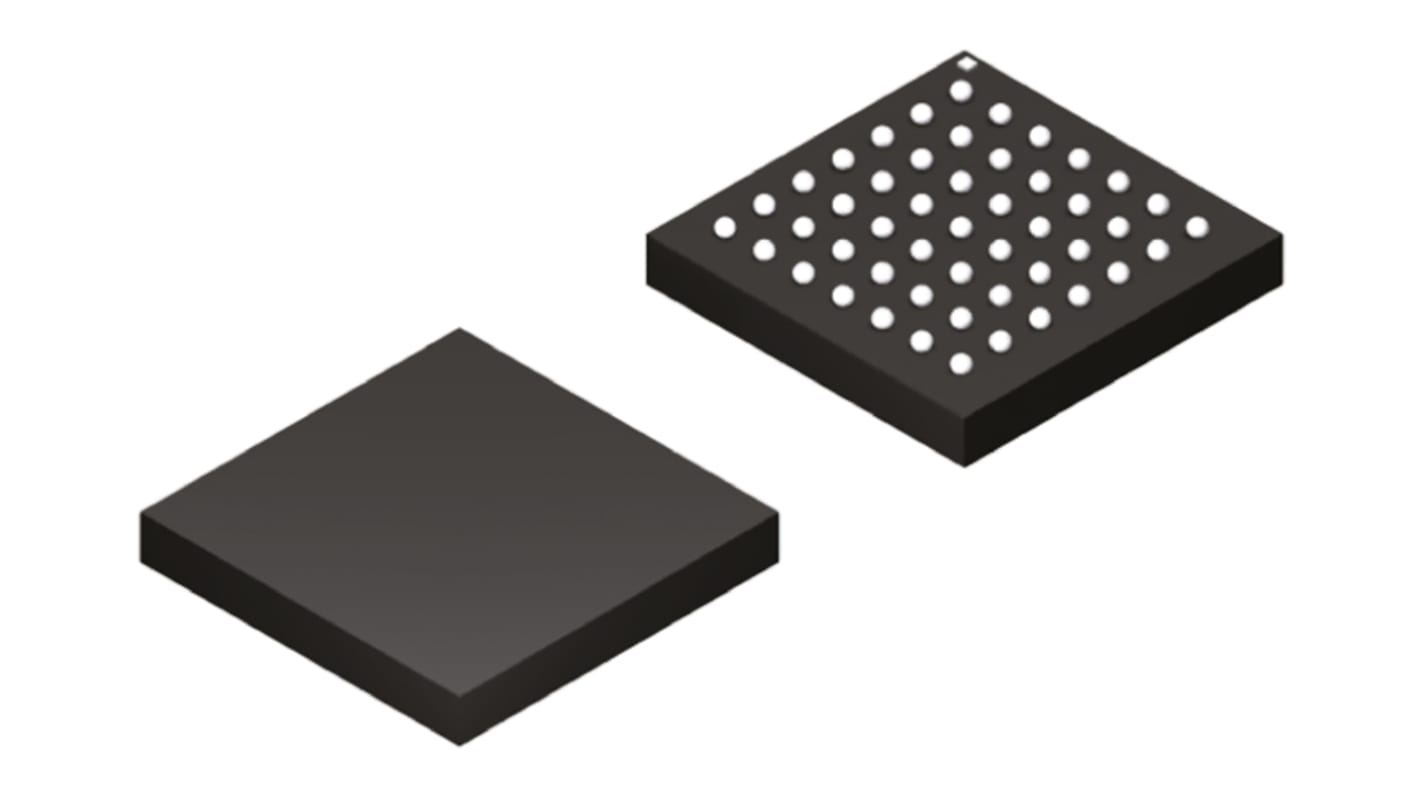

Lattice Semiconductor FPGA iCE40 LP/HX 1280 Zellen 160 Einh. UCBGA 49-Pin 1280Register 64 kB

- RS Best.-Nr.:

- 772-0085P

- Herst. Teile-Nr.:

- iCE40LP1K-CM49

- Hersteller:

- Lattice Semiconductor

Derzeit nicht erhältlich

Wir wissen nicht, ob wir diesen Artikel noch einmal auf Lager haben werden. RS beabsichtigt, ihn bald aus dem Sortiment zu nehmen.

- RS Best.-Nr.:

- 772-0085P

- Herst. Teile-Nr.:

- iCE40LP1K-CM49

- Hersteller:

- Lattice Semiconductor

Technische Daten des gezeigten Artikels

Datenblätter und Anleitungen

Rechtliche Anforderungen

Informationen zur Produktgruppe

Finden Sie ähnliche Produkte, indem Sie ein oder mehrere Eigenschaften auswählen.

Alle auswählen | Eigenschaft | Wert |

|---|---|---|

| Marke | Lattice Semiconductor | |

| Serie | iCE40 LP/HX | |

| Produkt Typ | FPGA | |

| Anzahl der Logik-Zellen | 1280 | |

| Anzahl der Logik-Einheiten | 160 | |

| Anzahl der Register | 1280 | |

| Montageart | Oberfläche | |

| Gehäusegröße | UCBGA | |

| Minimale Versorgungsspannung | 1.14V | |

| Pinanzahl | 49 | |

| Maximale Versorgungsspannung | 1.26V | |

| Anzahl der RAM Bits | 64kB | |

| Betriebstemperatur min. | -40°C | |

| Maximale Betriebstemperatur | 85°C | |

| Höhe | 0.9mm | |

| Länge | 3mm | |

| Normen/Zulassungen | Halogen Free | |

| Automobilstandard | Nein | |

| Alle auswählen | ||

|---|---|---|

Marke Lattice Semiconductor | ||

Serie iCE40 LP/HX | ||

Produkt Typ FPGA | ||

Anzahl der Logik-Zellen 1280 | ||

Anzahl der Logik-Einheiten 160 | ||

Anzahl der Register 1280 | ||

Montageart Oberfläche | ||

Gehäusegröße UCBGA | ||

Minimale Versorgungsspannung 1.14V | ||

Pinanzahl 49 | ||

Maximale Versorgungsspannung 1.26V | ||

Anzahl der RAM Bits 64kB | ||

Betriebstemperatur min. -40°C | ||

Maximale Betriebstemperatur 85°C | ||

Höhe 0.9mm | ||

Länge 3mm | ||

Normen/Zulassungen Halogen Free | ||

Automobilstandard Nein | ||

Anwenderprogrammierbare Steuergatterarrays (FPGA), Gitterhalbleiter

Ein FPGA ist ein Halbleitergerät, die aus einer Matrix aus konfigurierbaren Logikblöcke (CLBs) bestehen und durch programmierbare Verbindungen miteinander verbunden sind. Der Benutzer bestimmt diese Verbindungen durch die Programmierung eines SRAM. Ein CLB kann einfach (UND-, ODER-Gatter usw.) oder komplex (ein RAM-Block) sein. Der FPGA ermöglicht Designänderungen, auch nachdem das Gerät auf eine Leiterplatte gelötet wurde.

Verwandte Links

- Lattice Semiconductor FPGA iCE40 LP/HX 1280 Zellen 160 Einh. UCBGA 49-Pin 1280Register 64 kB

- Lattice Semiconductor FPGA iCE40 1280 Zellen 160 Einh. VQFP 100-Pin 1280Register 64000 bit

- Lattice Semiconductor FPGA iCE40 3520 Zellen 440 Einh. TQFP 144-Pin 3520Register 80000 bit

- Lattice Semiconductor Kabelmuffe Programmierer und In-Circuit-Emulator Programmierer

- Lattice Semiconductor Komplexes programmierbares Logikgerät MachXO2 78 I/O 7.24 ns Im Betrieb programmierbar TQFP

- Lattice Semiconductor Komplexes programmierbares Logikgerät ispMACH 64 Makrozellen 32 I/O EEPROM 7.5 ns Im Betrieb

- Lattice Semiconductor Komplexes programmierbares Logikgerät ispMACH 32 Makrozellen 30 I/O EEPROM 7.5 ns Im Betrieb

- Lattice Semiconductor Komplexes programmierbares Logikgerät ispMACH 32 Makrozellen 32 I/O EEPROM 7.5 ns Im Betrieb